今回はMOS構造について解説していきます。MOS構造ではその特殊な構造ゆえに特殊な現象が起こります。

MOSとは?

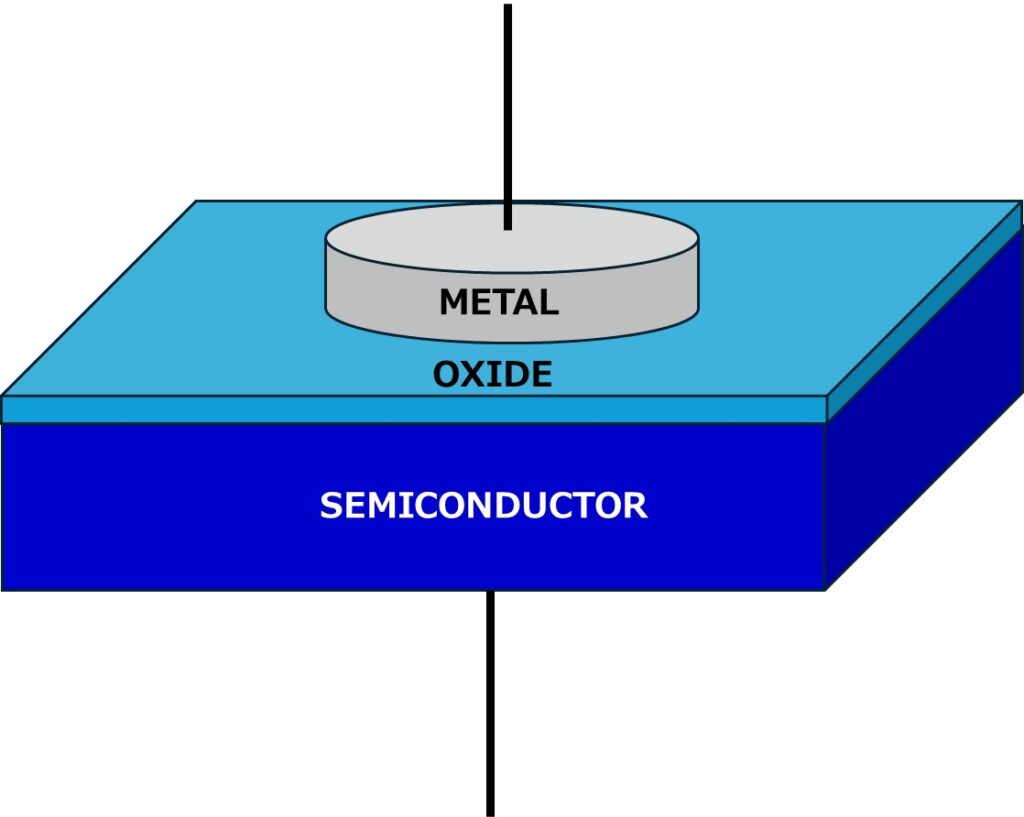

MOSはMetal-Oxide-Semiconductorの略で、半導体と金属で酸化物を挟んだ構造になります。

ダイオードは電荷を貯めることができるデバイスでした、MOSダイオードはMOSキャパシタとも呼ばれ、一言でいうと、

電圧によって容量の変調可能なキャパシタンス

です。

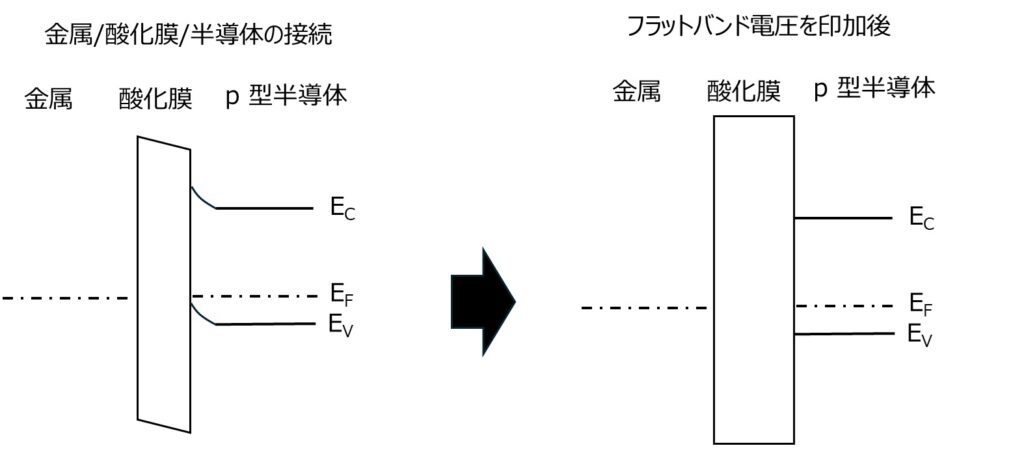

フラットバンド電圧とは?

MOSを理解する上でフラットバンド電圧を理解する必要があります。

フェルミエネルギーの異なる材料を接合させたとき、そのフェルミエネルギーが一致するようにキャリアが拡散する為、今回のような金属/酸化物/半導体という構造の場合それぞれバンドギャップや仕事関数が異なるためバンドの曲がりという現象が起きます。

この曲がったバンドを元に戻すために必要な電圧がフラットバンド電圧と呼びます。

バンドをフラットにするために必要な電圧ということでフラットバンド電圧になります。

MOSダイオードの原理~抑えるべきは5種類の動作モード~

以下の図のように金属側からp型の半導体側に電圧をかけた場合を考えます。

MOS構造ではフラットバンド電圧という概念が存在します。

主に5つの状況だけ覚えておけばMOSダイオードに関しては問題ありません!

1.Vg<VFBの時 (蓄積状態)

負の電圧を金属側にかける時、半導体側には+の電荷つまり陽子が半導体と酸化膜の界面に溜まることになります。

この時、電子が金属/酸化膜の界面に、正孔は酸化膜/半導体の界面にたまります。電荷をためる能力である容量は酸化膜の厚みで決まります。

つまり酸化膜の膜厚で静電容量が決まります。

$$C=d\frac{ε}{t:酸化膜厚}$$

2.Vg=VFBの時(フラットバンド電圧の状態)

この場合、バンドの曲がりはありませんので、一般的な平行板コンデンサとして考えることが可能です。この場合も酸化膜の厚みが空乏層の大きさです。

ただ実際は少し容量が下がります。この理由はこの記事の後半で少し解説します。

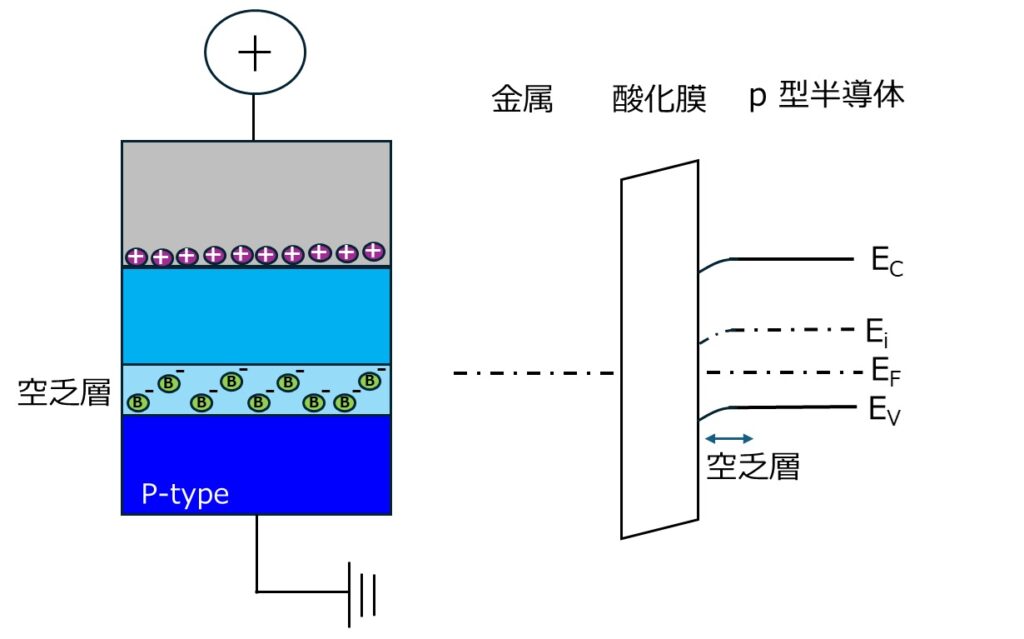

3.Vg>VFB(空乏状態)

この時半導体層には酸化膜との界面に+の電荷が引きつけられます。しかしバンドの曲がりを助長する電圧を印加していることに注意してください。つまり空乏層が伸びます。

p型はキャリアが正孔です。電子が界面に集まるということは、言い換えると界面付近の半導体層が極性を持たなくなり(4価になり)空乏層になってしまいます。ということで空乏層の大きさ分容量が大きくなります。

この状態は表面側に小数キャリアである電子が集まるので反転状態と呼ばれます。

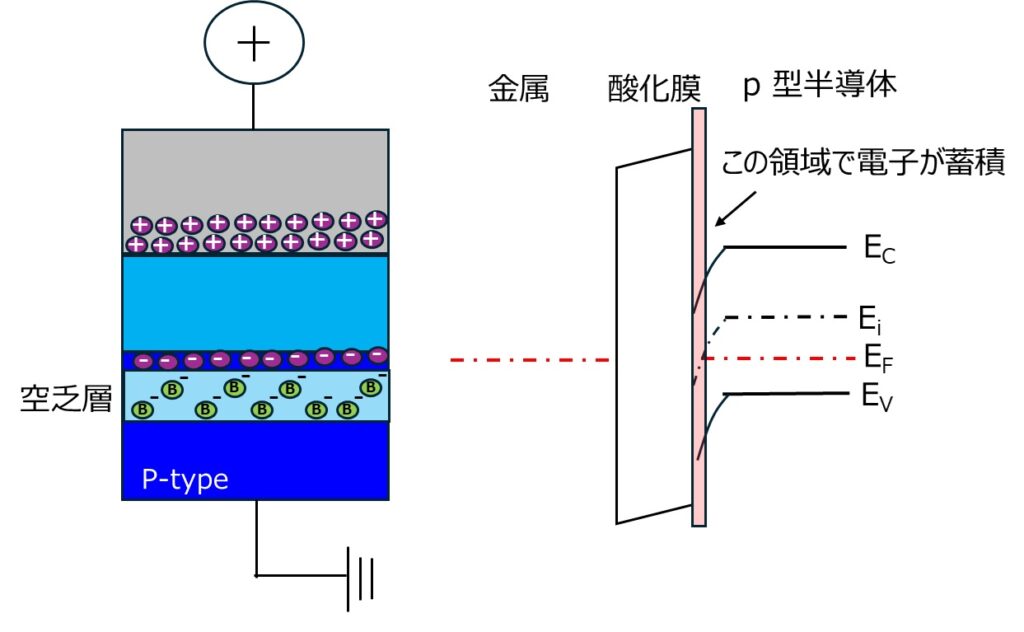

4.Vg>Vth(弱い反転状態)

この時にはバンドの曲がりが大きくなり界面付近で伝導帯がフェルミレベルを下回る領域が出てきます。したがって電子が貯まります。

フェルミエネルギーの位置は印加する電圧の大きさによって決まるので、言い換えると容量自体も印加電圧で決まってくるということになります。

この反転状態が生じるをVgを閾値電圧と呼び、Vthと書きます。

5.Vg>>Vth(強い反転)

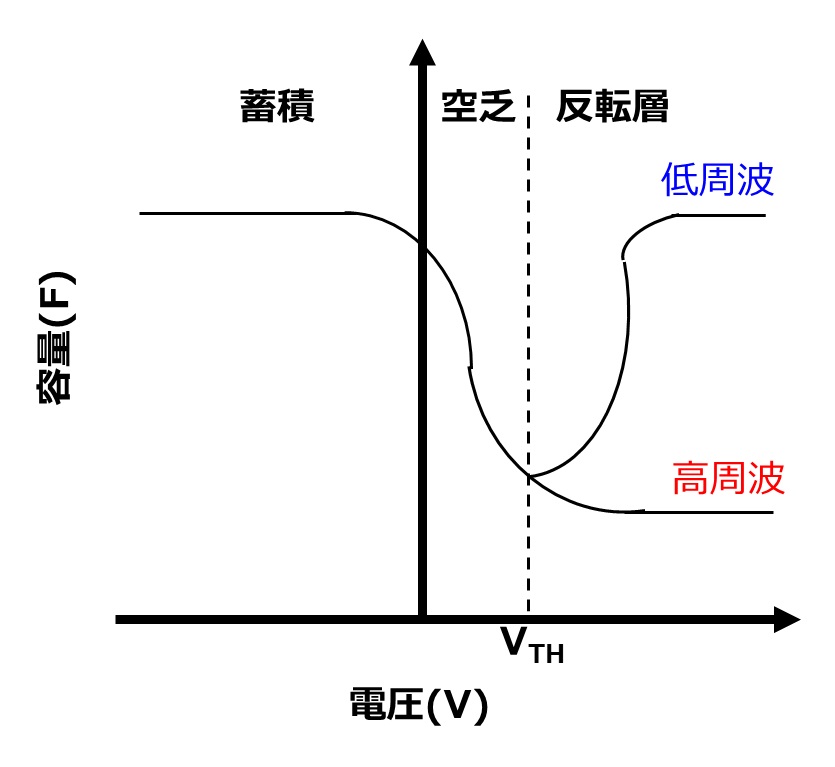

この領域では周波数によって容量が変化してくる領域です。

低周波の場合

Q=CVである為、

$$C=dQ/dV$$

Vの変化に対して電荷の変化が段々と大きくなる領域ですので高周波の場合,容量のCはどんどん増加していきます。

一方高周波では

反転層で生じる電子の発生と再結合の影響が大きく電荷密度の増減が電圧変化に追従しなくなり、容量としての変化はしなくなります。

MOSダイオードのCV特性

上で説明した状況を整理すると以下のようなCV曲線が得られます。

閾値電圧を超えてから電圧源の周波数帯でCV特性が変化します。

MOS構造の作り方

MOS構造の作り方ですが、p型 or n型のSi基板を熱酸化して酸化膜を作ります。

(熱酸化では膜質の良い酸化膜を正確な膜厚で作ることが出来ます。)

その上から導電性の高めたpoly-Siあるいは金属Al を製膜します。金属材料は仕事関数で種類を変えます。

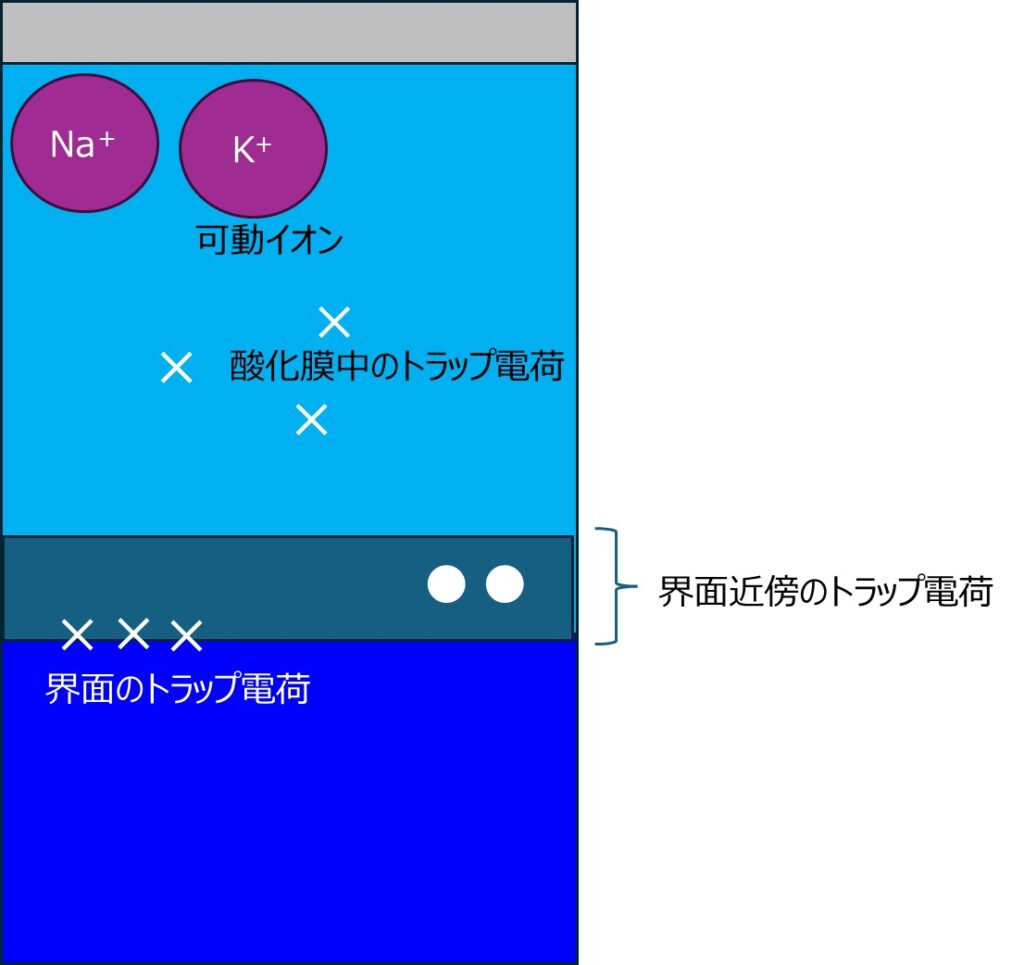

MOSダイオードに存在する実効界面電荷

理想的には上にあげたように、膜厚や電圧で容量が変わってきます。しかし実際は様々な原因で計算通りの容量になりません。

主に以下の4種類の電荷が存在することが原因となります。

・界面でのトラップ電荷

Si/SiO2のような半導体と酸化膜の界面では格子定数の違いから界面準位と呼ばれる準位が形成されます。ここに捕獲される電荷を固定電荷と呼びます。これは上記理由からSi(100)やSi(111)など面方位で値が大きく変わることが知られています。

・界面近傍の固定電荷

Si/SiO2 界面から3nm付近の部分では界面ポテンシャルの影響で理想通りの電荷の移動が出来ません。この部分では電荷が固定されてしまうため注意が必要です。

・酸化膜中のトラップ電荷

酸化膜中に存在する欠陥に起因する電荷です。これは固定電荷と呼ばれることが多く、酸化条件やアニール条件で変わってくる値になります。

・可動イオン電荷

Naなどのアルカリ金属類は高温(100℃)や高電界条件で酸化膜中を動くことで知られています。そのためC-V特性中のspecに影響してしまいます。そのためSiプロセスでは酸化膜に不純物を入れないように細心の注意を払う必要があります。

まとめ

MOSキャパシタは5つの状態に分けることが出来ます。

1.蓄積状態

2.フラット状態

3:空亡状態

4:弱い反転状態

5:強い反転状態→高周波 or 低周波

上記5つの状態を組合わせることで容量を制御可能なデバイスになります。